Usi Serial Interface

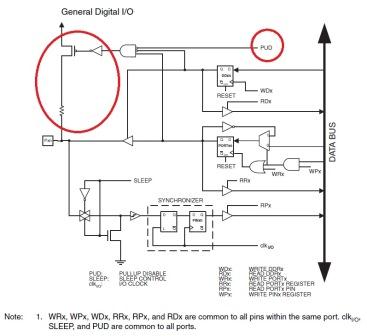

HTB1Wa9KRXXXXXaFXXXXq6xXFXXXn/WiFi-USI-module-Taiwan-MR09-Marvell8686-SPI-and-SDIO-interface-STM32-driver.jpg' alt='Usi Serial Interface' title='Usi Serial Interface' />Atmel AVR Wikipedia. This article needs attention from an expert in computer engineering. Cheque Printing Software Free Full here. The specific problem is Structure. Wiki. Project Computer engineering may be able to help recruit an expert. July 2. AVR is a family of microcontrollers developed by Atmel beginning in 1. HTB1Nlh3LXXXXXc1apXXq6xXFXXXE/220743542/HTB1Nlh3LXXXXXc1apXXq6xXFXXXE.jpg' alt='Usi Serial Interface' title='Usi Serial Interface' /> Cypress WiFi Bluetooth combos integrate IEEE 802. WLAN Bluetooth in a singlechip solution for smallformfactor IoT designs. Introduction ATTiny USI I2C Introduction a Powerful, Fast, and Convenient Communication Interface for Your ATTiny Projects Here are the latest articles published on Toms Hardware. See the latest news, reviews and roundups and access our tech archives. Micro Center Web Store You are currently browsing the products available on our web store. If you would like to choose a store location, please do so below. These are modified Harvard architecture. RISC single chip microcontrollers. AVR was one of the first microcontroller families to use on chip flash memory for program storage, as opposed to one time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time. AVR microcontrollers find many applications as embedded systems they are also used in the Arduino line of open source board designs. Brief historyeditThe AVR architecture was conceived by two students at the Norwegian Institute of Technology NTH,1 Alf Egil Bogen2 and Vegard Wollan. The original AVR MCU was developed at a local ASIC house in Trondheim, Norway, called Nordic VLSI at the time, now Nordic Semiconductor, where Bogen and Wollan were working as students. It was known as a RISC Micro RISCcitation needed and was available as silicon IPbuilding block from Nordic VLSI. When the technology was sold to Atmel from Nordic VLSI, the internal architecture was further developed by Bogen and Wollan at Atmel Norway, a subsidiary of Atmel. MSP430x2xx Family Users Guide Literature Number SLAU144J December 2004 Revised July 2013. The designers worked closely with compiler writers at IAR Systems to ensure that the AVR instruction set provided efficient compilation of high level languages. Atmel says that the name AVR is not an acronym and does not stand for anything in particular. The creators of the AVR give no definitive answer as to what the term AVR stands for. However, it is commonly accepted that AVR stands for Alf and Vegards RISC processor. Note that the use of AVR in this article generally refers to the 8 bit RISC line of Atmel AVR Microcontrollers. Among the first of the AVR line was the AT9. S8. 51. 5, which in a 4. DIP package has the same pinout as an 8. The polarity of the RESET line was opposite 8. RESET, while the AVR has an active low RESET, but other than that the pinout was identical. The AVR 8 bit microcontroller architecture was introduced in 1. By 2. 00. 3, Atmel had shipped 5. AVR flash microcontrollers. The Arduino platform for simple electronics projects was released in 2. ATmega. 8 AVR microcontrollers. Device overvieweditThe AVR is a modified Harvard architecture machine, where program and data are stored in separate physical memory systems that appear in different address spaces, but having the ability to read data items from program memory using special instructions. Basic familieseditAVRs are generally classified into following tiny. AVR the ATtiny series. KB program memory. Limited peripheral setmega. AVR the ATmega series. KB program memory. Extended instruction set multiply instructions and instructions for handling larger program memoriesExtensive peripheral set. XMEGA the ATxmega series. HTB1CamXLXXXXXbfaXXXq6xXFXXX0/220743542/HTB1CamXLXXXXXbfaXXXq6xXFXXX0.jpg' alt='Usi Serial Interface' title='Usi Serial Interface' />KB program memory. A4, A3, A13. 2 pin package XMEGA E XMEGA8. E5Extended performance features, such as DMA, Event System, and cryptography support. Extensive peripheral set with ADCs. The MSP430 is a mixedsignal microcontroller family from Texas Instruments. Built around a 16bit CPU, the MSP430 is designed for low cost and, specifically, low. View and Download Printronix Integrated Network Interface Card user manual online. Printronix Integrated Network Interface Card Users Manual. Integrated Network. TIs mspexp430g2 evaluation module evaluation board helps move your designs from prototype to production. EVM description and features provided along with. Syntax vendor vendorname device devicename single tab interface interfacename. Application specific AVRmega. AVRs with special features not found on the other members of the AVR family, such as LCD controller, USB controller, advanced PWM, CAN, etc. FPSLIC AVR with FPGAFPGA 5k to 4. SRAM for the AVR program code, unlike all other AVRs. Intel Graphics Card Download Windows 7. AVR core can run at up to 5. MHz73. 2 bit AVRs. In 2. 00. 6, Atmel released microcontrollers based on the 3. AVR3. 2 architecture. This is a completely different architecture unrelated to the 8 bit AVR, intended to compete with the ARM based processors. It has a 3. 2 bit data path, SIMD and DSP instructions, along with other audio and video processing features. The instruction set is similar to other RISC cores, but it is not compatible with the original AVR nor any of the various ARM cores. Device architectureeditFlash, EEPROM, and SRAM are all integrated onto a single chip, removing the need for external memory in most applications. Sage Line 50 Serial Number Activation Key on this page. Some devices have a parallel external bus option to allow adding additional data memory or memory mapped devices. Almost all devices except the smallest Tiny. AVR chips have serial interfaces, which can be used to connect larger serial EEPROMs or flash chips. Program memoryeditProgram instructions are stored in non volatileflash memory. Although the MCUs are 8 bit, each instruction takes one or two 1. The size of the program memory is usually indicated in the naming of the device itself e. ATmega. 64x line has 6. KB of flash, while the ATmega. KB. There is no provision for off chip program memory all code executed by the AVR core must reside in the on chip flash. However, this limitation does not apply to the AT9. FPSLIC AVRFPGA chips. Internal data memoryeditThe data address space consists of the register file, IO registers, and SRAM. Some small models also map the program ROM into the data address space, but larger models do not. Internal registersedit. Atmel ATxmega. 12. A1 in 1. 00 pin TQFP package. The AVRs have 3. 2 single byteregisters and are classified as 8 bit RISC devices. In the tiny. AVR and mega. AVR variants of the AVR architecture, the working registers are mapped in as the first 3. F1. 6, followed by 6. IO registers 0. F1. In devices with many peripherals, these registers are followed by 1. IO registers, only accessible as memory mapped IO 0. FF1. 6. Actual SRAM starts after these register sections, at address 0. IO, at 0. 10. 01. Even though there are separate addressing schemes and optimized opcodes for accessing the register file and the first 6. IO registers, all can also be addressed and manipulated as if they were in SRAM. The very smallest of the tiny. AVR variants use a reduced architecture with only 1. IO memory begins at address 0. SRAM. In addition, these devices have slight deviations from the standard AVR instruction set. Most notably, the direct loadstore instructions LDSSTS have been reduced from 2 words 3. IO and SRAM to 1. Conversely, the indirect load instructions LD 1. Flash and configuration bits therefore, the LPM instruction is unnecessary and omitted. In the XMEGA variant, the working register file is not mapped into the data address space as such, it is not possible to treat any of the XMEGAs working registers as though they were SRAM. Instead, the IO registers are mapped into the data address space starting at the very beginning of the address space. Additionally, the amount of data address space dedicated to IO registers has grown substantially to 4. FFF1. 6. As with previous generations, however, the fast IO manipulation instructions can only reach the first 6. IO register locations the first 3. Following the IO registers, the XMEGA series sets aside a 4. EEPROM to the data address space 1. FFF1. 6. The actual SRAM is located after these ranges, starting at 2. GPIO portseditEach GPIO port on a tiny or mega AVR drives up to eight pins and is controlled by three 8 bit registers DDRx, PORTx and PINx, where x is the port identifier. DDRx Data Direction Register, configures the pins as either inputs or outputs. PORTx Output port register. Sets the output value on pins configured as outputs. Enables or disables the pull up resistor on pins configured as inputs. PINx Input register, used to read an input signal.

Cypress WiFi Bluetooth combos integrate IEEE 802. WLAN Bluetooth in a singlechip solution for smallformfactor IoT designs. Introduction ATTiny USI I2C Introduction a Powerful, Fast, and Convenient Communication Interface for Your ATTiny Projects Here are the latest articles published on Toms Hardware. See the latest news, reviews and roundups and access our tech archives. Micro Center Web Store You are currently browsing the products available on our web store. If you would like to choose a store location, please do so below. These are modified Harvard architecture. RISC single chip microcontrollers. AVR was one of the first microcontroller families to use on chip flash memory for program storage, as opposed to one time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time. AVR microcontrollers find many applications as embedded systems they are also used in the Arduino line of open source board designs. Brief historyeditThe AVR architecture was conceived by two students at the Norwegian Institute of Technology NTH,1 Alf Egil Bogen2 and Vegard Wollan. The original AVR MCU was developed at a local ASIC house in Trondheim, Norway, called Nordic VLSI at the time, now Nordic Semiconductor, where Bogen and Wollan were working as students. It was known as a RISC Micro RISCcitation needed and was available as silicon IPbuilding block from Nordic VLSI. When the technology was sold to Atmel from Nordic VLSI, the internal architecture was further developed by Bogen and Wollan at Atmel Norway, a subsidiary of Atmel. MSP430x2xx Family Users Guide Literature Number SLAU144J December 2004 Revised July 2013. The designers worked closely with compiler writers at IAR Systems to ensure that the AVR instruction set provided efficient compilation of high level languages. Atmel says that the name AVR is not an acronym and does not stand for anything in particular. The creators of the AVR give no definitive answer as to what the term AVR stands for. However, it is commonly accepted that AVR stands for Alf and Vegards RISC processor. Note that the use of AVR in this article generally refers to the 8 bit RISC line of Atmel AVR Microcontrollers. Among the first of the AVR line was the AT9. S8. 51. 5, which in a 4. DIP package has the same pinout as an 8. The polarity of the RESET line was opposite 8. RESET, while the AVR has an active low RESET, but other than that the pinout was identical. The AVR 8 bit microcontroller architecture was introduced in 1. By 2. 00. 3, Atmel had shipped 5. AVR flash microcontrollers. The Arduino platform for simple electronics projects was released in 2. ATmega. 8 AVR microcontrollers. Device overvieweditThe AVR is a modified Harvard architecture machine, where program and data are stored in separate physical memory systems that appear in different address spaces, but having the ability to read data items from program memory using special instructions. Basic familieseditAVRs are generally classified into following tiny. AVR the ATtiny series. KB program memory. Limited peripheral setmega. AVR the ATmega series. KB program memory. Extended instruction set multiply instructions and instructions for handling larger program memoriesExtensive peripheral set. XMEGA the ATxmega series. HTB1CamXLXXXXXbfaXXXq6xXFXXX0/220743542/HTB1CamXLXXXXXbfaXXXq6xXFXXX0.jpg' alt='Usi Serial Interface' title='Usi Serial Interface' />KB program memory. A4, A3, A13. 2 pin package XMEGA E XMEGA8. E5Extended performance features, such as DMA, Event System, and cryptography support. Extensive peripheral set with ADCs. The MSP430 is a mixedsignal microcontroller family from Texas Instruments. Built around a 16bit CPU, the MSP430 is designed for low cost and, specifically, low. View and Download Printronix Integrated Network Interface Card user manual online. Printronix Integrated Network Interface Card Users Manual. Integrated Network. TIs mspexp430g2 evaluation module evaluation board helps move your designs from prototype to production. EVM description and features provided along with. Syntax vendor vendorname device devicename single tab interface interfacename. Application specific AVRmega. AVRs with special features not found on the other members of the AVR family, such as LCD controller, USB controller, advanced PWM, CAN, etc. FPSLIC AVR with FPGAFPGA 5k to 4. SRAM for the AVR program code, unlike all other AVRs. Intel Graphics Card Download Windows 7. AVR core can run at up to 5. MHz73. 2 bit AVRs. In 2. 00. 6, Atmel released microcontrollers based on the 3. AVR3. 2 architecture. This is a completely different architecture unrelated to the 8 bit AVR, intended to compete with the ARM based processors. It has a 3. 2 bit data path, SIMD and DSP instructions, along with other audio and video processing features. The instruction set is similar to other RISC cores, but it is not compatible with the original AVR nor any of the various ARM cores. Device architectureeditFlash, EEPROM, and SRAM are all integrated onto a single chip, removing the need for external memory in most applications. Sage Line 50 Serial Number Activation Key on this page. Some devices have a parallel external bus option to allow adding additional data memory or memory mapped devices. Almost all devices except the smallest Tiny. AVR chips have serial interfaces, which can be used to connect larger serial EEPROMs or flash chips. Program memoryeditProgram instructions are stored in non volatileflash memory. Although the MCUs are 8 bit, each instruction takes one or two 1. The size of the program memory is usually indicated in the naming of the device itself e. ATmega. 64x line has 6. KB of flash, while the ATmega. KB. There is no provision for off chip program memory all code executed by the AVR core must reside in the on chip flash. However, this limitation does not apply to the AT9. FPSLIC AVRFPGA chips. Internal data memoryeditThe data address space consists of the register file, IO registers, and SRAM. Some small models also map the program ROM into the data address space, but larger models do not. Internal registersedit. Atmel ATxmega. 12. A1 in 1. 00 pin TQFP package. The AVRs have 3. 2 single byteregisters and are classified as 8 bit RISC devices. In the tiny. AVR and mega. AVR variants of the AVR architecture, the working registers are mapped in as the first 3. F1. 6, followed by 6. IO registers 0. F1. In devices with many peripherals, these registers are followed by 1. IO registers, only accessible as memory mapped IO 0. FF1. 6. Actual SRAM starts after these register sections, at address 0. IO, at 0. 10. 01. Even though there are separate addressing schemes and optimized opcodes for accessing the register file and the first 6. IO registers, all can also be addressed and manipulated as if they were in SRAM. The very smallest of the tiny. AVR variants use a reduced architecture with only 1. IO memory begins at address 0. SRAM. In addition, these devices have slight deviations from the standard AVR instruction set. Most notably, the direct loadstore instructions LDSSTS have been reduced from 2 words 3. IO and SRAM to 1. Conversely, the indirect load instructions LD 1. Flash and configuration bits therefore, the LPM instruction is unnecessary and omitted. In the XMEGA variant, the working register file is not mapped into the data address space as such, it is not possible to treat any of the XMEGAs working registers as though they were SRAM. Instead, the IO registers are mapped into the data address space starting at the very beginning of the address space. Additionally, the amount of data address space dedicated to IO registers has grown substantially to 4. FFF1. 6. As with previous generations, however, the fast IO manipulation instructions can only reach the first 6. IO register locations the first 3. Following the IO registers, the XMEGA series sets aside a 4. EEPROM to the data address space 1. FFF1. 6. The actual SRAM is located after these ranges, starting at 2. GPIO portseditEach GPIO port on a tiny or mega AVR drives up to eight pins and is controlled by three 8 bit registers DDRx, PORTx and PINx, where x is the port identifier. DDRx Data Direction Register, configures the pins as either inputs or outputs. PORTx Output port register. Sets the output value on pins configured as outputs. Enables or disables the pull up resistor on pins configured as inputs. PINx Input register, used to read an input signal.